Les dernières informations poussent à penser que le processeur « Strix Halo » d’AMD n’est plus une hypothèse mais une réalité en devenir. Cette puce imposante est conçue pour concurrencer directement les solutions M3 Pro et M3 Max d’Apple, avec une orientation claire vers le marché des ordinateurs portables et ultraportables.

Strix Halo, un design pour de hautes performances graphiques

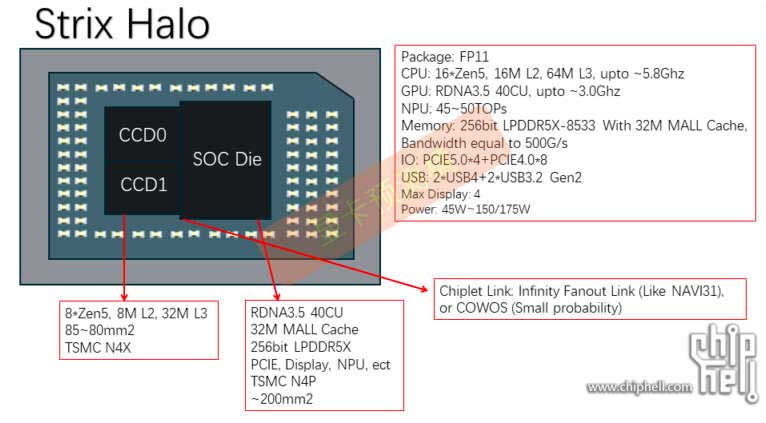

AMD vise à offrir des performances graphiques élevées sans nécessiter de carte graphique dédiée. Pour y parvenir, la société adopte une approche à base de chiplets, similaire à celle utilisée pour les processeurs « Raphael » pour PC de bureau et « Dragon Range » pour les offres mobiles en boîtier BGA.

Le processeur « Strix Halo » sera composé d’un ou deux CCD (Core Complex Die) contenant des cœurs de processeur, connectés à une grande unité centrale nommée SOC Die dans le diagramme. Cette unité se compose de deux modules principaux : un GPU intégré puissant (iGPU) et un NPU (Neural Processing Unit). L’objectif est d’éliminer le besoin de cartes graphiques traditionnelles sur le segment des performances.

Le « Strix Halo » sera livré dans un boîtier BGA nommé FP11, mesurant 37,5 mm x 45 mm. Ce format est nettement plus grand que les 25 mm x 40 mm du boîtier BGA FP8, utilisé par les processeurs mobiles « Strix Point », « Hawk Point » et « Phoenix ».

Le « Strix Halo » utilisera les mêmes CCD « Zen 5 » en 4 nm que ceux des processeurs de bureau « Granite Ridge » et mobiles « Fire Range ». Cette technologie de pointe promet des performances améliorées et une efficacité énergétique accrue, adaptée aux besoins des utilisateurs mobiles exigeants.

Strix Halo, des précisions

À ce stade, la finesse de gravure utilisée n’est pas connue, mais il est probable qu’AMD utilise du 4 nm pour la matrice d’E/S. Cette hypothèse est motivée par la présence d’un iGPU basé sur l’architecture RDNA 3.5, comprenant 20 processeurs de groupe de travail (WGP), soit 40 unités de calcul (CU), totalisant 2 560 processeurs de flux, 80 accélérateurs d’IA et 40 accélérateurs de Ray Tracing. En outre, un NPU basé sur l’architecture XDNA 2, capable de fournir une puissance entre 45 et 50 TOPs, est inclus pour répondre aux exigences de Microsoft afin d’être considéré comme un Copilot+ PC.

Une question demeure concernant l’interface mémoire de « Strix Halo ». Avoir 16 cœurs de processeur « Zen 5 » et un GPU de 40 unités de calcul partageant une interface mémoire DDR5 double canal classique, même à haute fréquence, pourrait ne pas être idéal. Dans ce cas, le CPU et l’iGPU souffriraient d’un manque de bande passante, affectant significativement les performances, sans oublier le NPU. L’inférence de l’IA est très sensible à la mémoire.

Une hypothèse non confirmée est qu’AMD pourrait envisager, en plus de l’interface LPDDR5X pour les cœurs du processeur, un câblage pour de la mémoire GDDR6. Même avec un bus de 128 bits et une vitesse de 20 Gbps, cela offrirait à l’iGPU une bande passante de 320 Go/s, suffisante pour les besoins du segment « performance ». Cela impliquerait qu’en plus des puces LPDDR5X, quatre puces GDDR6 seraient présentes sur le PCB.

Sources : Harukaze_5719 (Twitter), Olrak29 (Twitter)